# R5C841 PCI-CardBus/IEEE1394/SD Card /MemoryStick/xD/ExpressCard Data Sheet

## **REV. 1.10**

## RIGOH

| REVISION | DATE    | COMMENTS                                                                                                                  |  |  |  |  |  |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 0.60     | 7/24/03 | First Draft (described Overview, Block Diagram and Pin description only)                                                  |  |  |  |  |  |

| 0.70     | 9/10/03 | Addition of the regulator description (Spec 4) and the electrical characteristics Spec 5).                                |  |  |  |  |  |

| 0.80     | 11/6/03 | Change from NewCard to ExpressCard.<br>Mistakes in writing are corrected.                                                 |  |  |  |  |  |

| 1.00     | 1/30/04 | First Public Release<br>Mistakes in writing are corrected.                                                                |  |  |  |  |  |

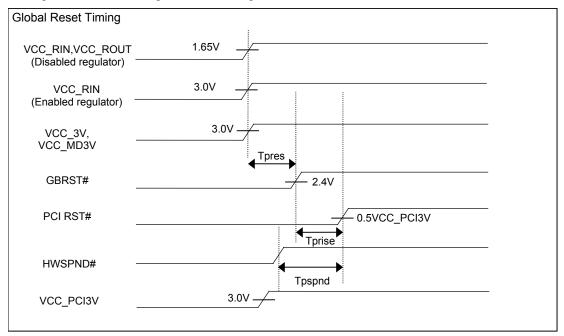

| 1.10     | 5/18/04 | Changes in the chart of Global Reset Timing (Ch. 5.3.6).<br>Deletion of the 2.5V power supply support for the core logic. |  |  |  |  |  |

#### -REVISION HISTORY-

#### 1 OVERVIEW

The R5C841 is a single chip solution offering five PCI functions (a PCI bus bridge to a PC Card, an IEEE 1394, an SD Card, a Memory Stick and an xD Picture Card) with an ExpressCard (USB Interface Type) switch.

- PC98/99/2001 compliant

- PC2001 Design Guide compliant (Subsystem ID, Subsystem Vendor ID)

- Compliant with ACPI and PCI Bus Power Management 1.1

- Support Global Reset

- Low Power consumption

- Low operating power consumption due to the improvement of Power Management

- Software Suspend mode compliant with ACPI

- Hardware Suspend

- CLKRUN#, CCLKRUN# support

- The core logic powered at 1.8V, the others powered at 3.3V

- PCI-CardBus/1394 Bridge/SD Card/Memory Stick/xD Picture Card/ExpressCard interface

- 1-slot PC Card

- 2 ports of IEEE1394

- MDIOxx pins shared by SD Card, Memory Stick and xD Picture Card

- Providing Ricoh's proprietary driver for Memory Stick and xD Picture Card

- ExpressCard (USB Interface Type) supported by the PC Card passive adapter

- PCI Bus Interface

- Compliant with PCI Local Bus Specification2.3

- The maximum frequency 33MHz

- PCI Master/Target protocol support

- PCI configuration space for each function

- 3.3V Interface (5V tolerant)

- CardBus PC card Bridge

- Compliant with PC Card Standard Release 8.1 Specification

- The maximum frequency 33MHz

- Support CardBus Master/Target protocol

- Support Memory Write Posting/ Read Prefetching

- Transfer transactions

- All memory read/write transaction (bi-direction)

- I/O read/write transaction (bi-direction)

- Configuration read/write transaction (PCI  $\rightarrow$  Card)

- 2 programmable memory windows

- 2 programmable I/O windows

- PC Card-16 Bridge

- Compliant with PC Card Standard Release 8.1 16-bit Specification

- 5 programmable memory windows

- 2 programmable I/O windows

- Compliant with i82365SL compatible register set/ExCA

- Support Legacy 16-bit mode (3E0, 3E2 I/O ports)

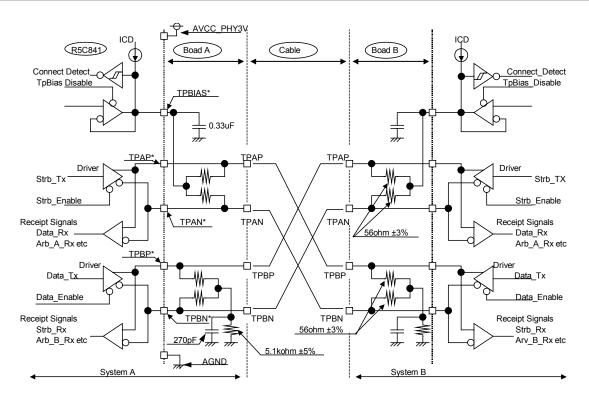

- ♦ IEEE1394 Interface

- Compliant with IEEE1394-1995 Standard Specification and IEEE1394a-2000 Standard Specification

- Compliant with 1394 OHCI Release 1.1/1.0 Standard Specification

- Support Cycle Master

- Provide the Asynchronous receive/transmit FIFO and isochronous receive/transmit FIFO

- Support Self-ID, physical DMA

- Data transmission rate of 100, 200 and 400Mbps

- 2 ports of 1394 Cable interface

- 24.576MHz crystal oscillator and Internal 393.216MHz PLL

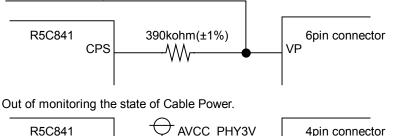

- Support Cable Power monitoring (CPS)

- Set Initial values of Power Class and CMC by PCI Configuration registers

- Small Card Interface

- SD Card

- Compliant with SD Memory Card Specification Version 1.01

- Compliant with SD Input/Output (SDIO) Card Specification Version 1.0

- Compliant with SD Host Controller Standard Specification Version 1.0

- Memory Stick

- Compliant with Memory Stick Standard Format Specification Version 1.4

- Compliant with Memory Stick PRO Format Specification Version 1.00

- xD Picture Card

- Compliant with xD Picture Card Specification Version 1.00

- Compliant with xD Picture Card Host Guideline Version 1.00

- Backward compatible with the Smart Media

- ExpressCard Interface

- Compliant with EXPRESSCARD STANDARD Draft Release 1.0 (USB Interface Type only)

- Pass USB signals from a USB-HOST to a Card Slot

- System Interrupt

- Support INTA#, INTB# and INTC# for PC system interrupt (Each unit is programmable.)

- Support Serialized IRQ

- IRQx support for ISA system interrupt

- Support Remote Wake Up by CSTSCHG

- Support an internal regulator to convert the 3.3V power into the power for the internal core logic

- Support Zoomed Video Port (Bypass type)

- Support PC Card LED, 1394 LED, SD LED, Memory Stick LED and xD Picture Card LED

- Support BAY function with the PC Card passive adapter

- Pin Compatible With: R5C811 (CSP1616-208) R5C821 (CSP1616-208) R5C821PA (CSP1616-208) R5C851 (CSP1616-208) R5C851PA (CSP1616-208)

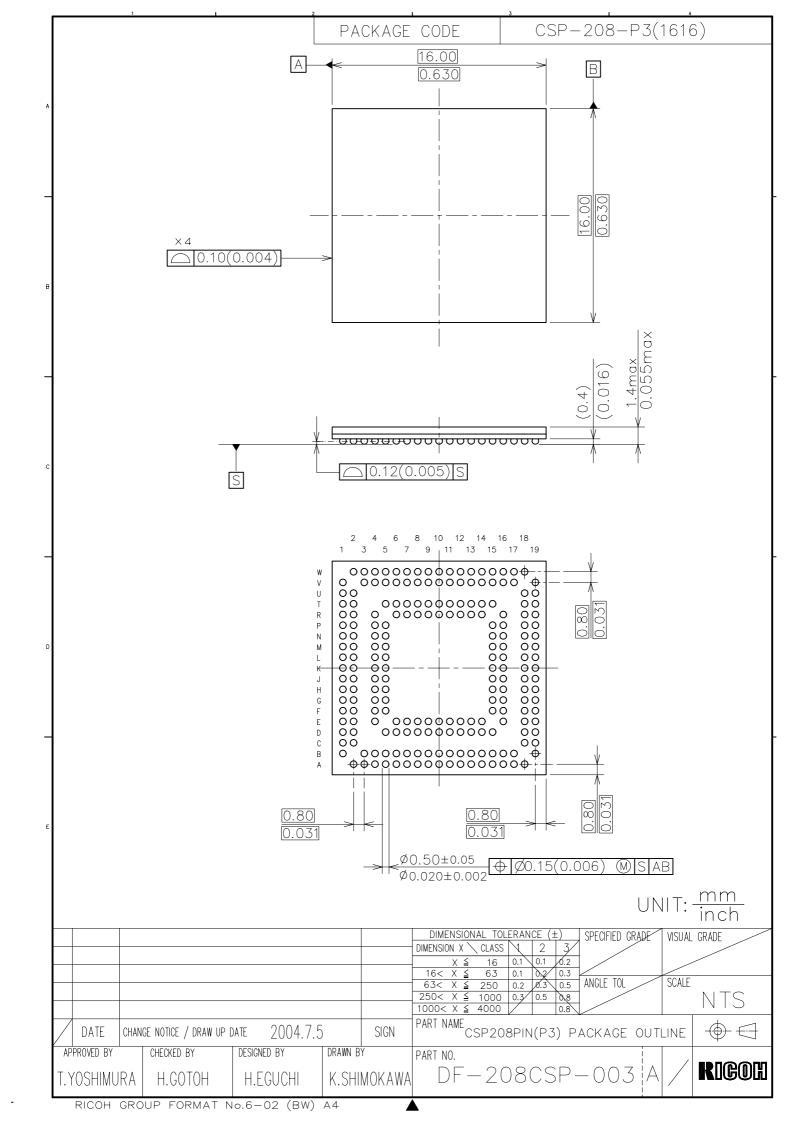

- Package

- 208pin CSP (size=16x16mm, pitch=0.8mm, t=1.4mm)

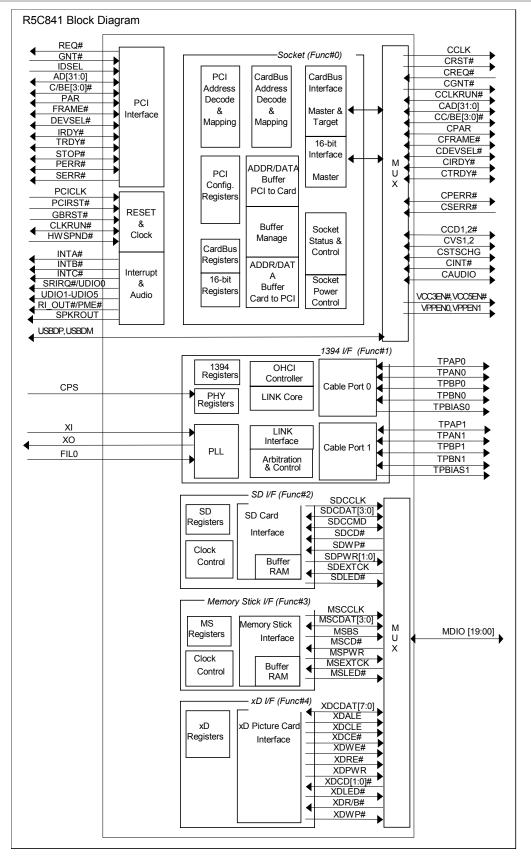

#### 2 BLOCK DIAGRAM

## 3 **PIN DESCRIPTION**

## 3.1 Pin Assignments (208 pin CSP)

• CSP Pin Assignment

**Bottom View**

|    | А              | В              | С           | D            | Е              | F           | G                | Н          | J                | K           | L            | М                  | Ν           | Р           | R             | Т            | U            | v            | W              |

|----|----------------|----------------|-------------|--------------|----------------|-------------|------------------|------------|------------------|-------------|--------------|--------------------|-------------|-------------|---------------|--------------|--------------|--------------|----------------|

| 1  | ×              | O<br>MDIO00    | O<br>NC     | O<br>NC      | O<br>NC        | O<br>SPKROU | O<br>T UDIO5     |            | GND              | O           |              | O<br>AD30          | O<br>AD26   |             | O<br>AD21     | O<br>AD19    | O<br>AD17    | O<br>AD16    | $\overline{\}$ |

| 2  | O<br>MDIO01    |                | O<br>NC     | O<br>NC      | O<br>NC        | O<br>HWSPNI | O<br>D#GBRST#    |            | O<br>INTA#       | O<br>INTC#  |              | O<br>AD31          | O<br>AD27   | O<br>C/BE3# | O<br>AD22     | O<br>AD20    | O<br>AD18    |              | O<br>C/BE2#    |

| 3  | O<br>MDIO02    | O<br>MDIO03    |             |              |                |             |                  |            |                  |             |              |                    |             |             |               |              |              | O<br>FRAME#  | VCC_<br>PCI3V  |

| 4  | VCC_<br>MD3V   | O<br>MDIO04    |             |              | O<br>NC        | O           | RI_OUT#/<br>PME# | O<br>UDIO3 | UDIO0/<br>SRIRQ# | O<br>INTB#  | O<br>PCIRST# | O<br>REQ#          | O<br>AD28   | O<br>AD24   | O<br>AD23     |              |              | O<br>IRDY#   | O<br>TRDY#     |

| 5  | O<br>MDIO05    | O<br>MDIO06    |             | O<br>MDIO07  |                | VCC_3V      | VCC_3V           | O<br>UDIO4 | GND              | GND         | O<br>CLKRUN# | O<br>GNT#          | O<br>AD29   | O<br>AD25   |               | O<br>DEVSEL# |              | O<br>STOP#   | O<br>PERR#     |

| 6  | O<br>MDIO08    | O<br>MDIO09    |             | O<br>MDIO10  | O<br>MDIO11    |             |                  |            |                  |             |              |                    |             |             | VCC_<br>RIN   | O<br>SERR#   |              | O<br>PAR     | O<br>C/BE1#    |

| 7  | O<br>MDIO12    | O<br>MDIO13    |             | O<br>MDIO14  | O<br>MDIO15    |             |                  |            |                  |             |              |                    |             |             | O<br>REGEN#   | O<br>AD15    |              | O<br>AD14    | O<br>AD13      |

| 8  | O<br>MDIO16    | O<br>MDIO17    |             | O<br>MDIO18  | O<br>MDIO19    |             |                  |            |                  |             |              |                    |             |             | O<br>AD12     | O<br>AD11    |              | O<br>AD10    | O<br>AD9       |

| 9  | AGND           | AGND           |             | AGND         | GND            |             |                  |            |                  |             |              |                    |             |             | O<br>AD8      | O<br>C/BE0#  |              | O<br>AD7     | O<br>AD6       |

| 10 | O<br>TPAN1     | O<br>TPAP1     |             | O<br>TPBIAS1 | AVCC_<br>PHY3V |             |                  |            |                  |             |              |                    |             |             | GND           | GND          |              | <b>GND</b>   | GND            |

| 11 | O<br>TPBN1     | O<br>TPBP1     |             | O<br>CPS     | AVCC_<br>PHY3V |             |                  |            |                  |             |              |                    |             |             | VCC<br>PCI3V  | O<br>AD5     |              | O<br>AD4     | O<br>AD3       |

| 12 | O<br>TPAN0     | O<br>TPAP0     |             | O<br>TPBIAS0 | O<br>NC        |             |                  |            |                  |             |              |                    |             |             | VCC_<br>PCI3V | O<br>AD2     |              | O<br>AD1     | O<br>AD0       |

| 13 | O<br>TPBN0     | O<br>TPBP0     |             | O<br>VREF    | VCC_<br>RIN    |             |                  |            |                  |             |              |                    |             |             | O<br>VCC5EN#  | O<br>VCC3EN# |              | O<br>VPPEN0  | O<br>VPPEN1    |

| 14 | O<br>FIL0      | OREXT          |             | AGND         |                |             |                  |            |                  |             |              |                    |             |             | O<br>CDATA3   | O<br>CD1#    |              | OUSBDP       |                |

| 15 | AGND           | AGND           |             | O<br>CD2#    |                | O<br>CADR2  | O<br>CADR4       | O<br>CADR6 | O<br>CADR24      | O<br>CADR15 | GND          | O<br>WE#           | O<br>CADR13 | O<br>CADR8  |               | O<br>CDATA4  |              | O<br>CDATA11 | O<br>CDATA5    |

| 16 | O<br>XI        | O<br>xo        |             |              | O<br>CADR0     | O<br>REG#   | O<br>WAIT#       | O<br>VS2#  | O<br>CADR7       | O<br>CADR23 | O<br>CADR22  | O<br>CADR20        | O<br>CADR18 | O<br>CADR17 | O<br>VS1#     |              |              | O<br>CDATA12 | O<br>CDATA6    |

| 17 | AVCC_<br>PHY3V | AVCC_<br>PHY3V |             |              |                |             |                  |            |                  |             |              |                    |             |             |               |              |              | O<br>CDATA13 | O<br>CDATA7    |

| 18 | WP/            | FILOV          | O<br>CDATA9 | O<br>CDATA8  | O<br>BVD1      | O<br>CADR1  | O<br>CADR3       | O<br>CADR5 | O<br>CADR25      | O<br>CADR12 | O<br>CADR21  | O<br>RDY/<br>IREQ# | O<br>CADR14 | O<br>IORD#  | O<br>CARD11   | O<br>CE2#    | O<br>CDATA15 |              | O<br>CDATA14   |

| 19 |                | O<br>CDATA10   | O<br>CDATA2 | O<br>CDATA1  | O<br>CDATA0    | O<br>BVD2   | O<br>INPACK#     | O<br>RESET | VCC_3V           | VCC_3V      | O<br>CADR16  | GND                | O<br>CADR19 | O<br>IOWR#  | O<br>CADR9    | O<br>OE#     | O<br>CADR10  | O<br>CE1#    |                |

| • | CSP | Pin | List |

|---|-----|-----|------|

|---|-----|-----|------|

| Dell |              | Dell | Signal Marra | Dell | Cignal Marga |      | Cignal Marsa |

|------|--------------|------|--------------|------|--------------|------|--------------|

| Ball | Signal Name  |

| F4   | TEST         | V5   | STOP#        | T19  | OE#          | C19  | CDATA2       |

| F2   | HWSPND#      | W5   | PERR#        | R16  | VS1#         | B19  | CDATA10      |

| F1   | SPKROUT      | Т6   | SERR#        | R18  | CADR11       | A18  | WP/IOIS16#   |

| G4   | RI_OUT#/PME# | V6   | PAR          | R19  | CADR9        | D15  | CD2#         |

| G2   | GBRST#       | W6   | C/BE1#       | P18  | IORD#        | E8   | MDIO19       |

| G1   | UDIO5        | Τ7   | AD15         | P19  | IOWR#        | D8   | MDIO18       |

| H5   | UDIO4        | V7   | AD14         | P15  | CADR8        | B8   | MDIO17       |

| H4   | UDIO3        | W7   | AD13         | P16  | CADR17       | A8   | MDIO16       |

| H2   | UDIO2        | R8   | AD12         | N15  | CADR13       | E7   | MDIO15       |

| H1   | UDIO1        | T8   | AD11         | N16  | CADR18       | D7   | MDIO14       |

| J4   | UDIO0/SRIRQ# | V8   | AD10         | N18  | CADR14       | B7   | MDIO13       |

| J2   | INTA#        | W8   | AD9          | N19  | CADR19       | A7   | MDIO12       |

| K4   | INTB#        | R9   | AD8          | M15  | WE#          | E6   | MDIO11       |

| K2   | INTC#        | Т9   | C/BE0#       | M16  | CADR20       | D6   | MDIO10       |

| L5   | CLKRUN#      | V9   | AD7          | M18  | RDY/IREQ#    | B6   | MDIO09       |

| L4   | PCIRST#      | W9   | AD6          | L16  | CADR22       | A6   | MDIO08       |

| K1   | PCICLK       | T11  | AD5          | L18  | CADR21       | D5   | MDIO07       |

| M5   | GNT#         | V11  | AD4          | L19  | CADR16       | B5   | MDIO06       |

| M4   | REQ#         | W11  | AD3          | K15  | CADR15       | A5   | MDIO05       |

| M2   | AD31         | T12  | AD2          | K16  | CADR23       | B4   | MDIO04       |

| M1   | AD30         | V12  | AD1          | K18  | CADR12       | B3   | MDIO03       |

| N5   | AD29         | W12  | AD0          | J15  | CADR24       | A3   | MDIO02       |

| N4   | AD28         | R13  | VCC5EN#      | J16  | CADR7        | A2   | MDIO01       |

| N2   | AD27         | T13  | VCC3EN#      | J18  | CADR25       | B1   | MDIO00       |

| N1   | AD26         | V13  | VPPEN0       | H15  | CADR6        | B16  | XO           |

| P5   | AD25         | W13  | VPPEN1       | H16  | VS2#         | A16  | XI           |

| P4   | AD24         | V14  | USBDP        | H18  | CADR5        | B14  | REXT         |

| P2   | C/BE3#       | W14  | USBDM        | H19  | RESET        | A14  | FIL0         |

| P1   | IDSEL        | R14  | CDATA3       | G15  | CADR4        | D13  | VREF         |

| R4   | AD23         | T14  | CD1#         | G16  | WAIT#        | B13  | TPBP0        |

| R2   | AD22         | T15  | CDATA4       | G18  | CADR3        | A13  | TPBN0        |

| R1   | AD21         | V15  | CDATA11      | G19  | INPACK#      | D12  | TPBIAS0      |

| T2   | AD20         | W15  | CDATA5       | F15  | CADR2        | B12  | TPAP0        |

| T1   | AD19         | V16  | CDATA12      | F16  | REG#         | A12  | TPAN0        |

| U2   | AD18         | W16  | CDATA6       | F18  | CADR1        | D11  | CPS          |

| U1   | AD17         | V17  | CDATA13      | F19  | BVD2         | B11  | TPBP1        |

| V1   | AD16         | W17  | CDATA7       | E16  | CADR0        | A11  | TPBN1        |

| W2   | C/BE2#       | W18  | CDATA14      | E18  | BVD1         | D10  | TPBIAS1      |

| V3   | FRAME#       | V19  | CE1#         | E19  | CDATA0       | B10  | TPAP1        |

| V4   | IRDY#        | U18  | CDATA15      | D18  | CDATA8       | A10  | TPAN1        |

| W4   | TRDY#        | U19  | CADR10       | D19  | CDATA1       | R7   | REGEN#       |

| T5   | DEVSEL#      | T18  | CE2#         | C18  | CDATA9       |      |              |

| Pin Name   | Ball#              | Pin Name | Ball#                          |  |

|------------|--------------------|----------|--------------------------------|--|

| VCC_PCI3V  | W3, R11, R12       | AGND     | A9, B9, D9, D14, A15, B15      |  |

| VCC_3V     | F5, G5, J19, K19   | GND      | J1, J5, K5, E9, R10, T10, V10, |  |

| VCC_MD3V   | A4                 | GND      | W10, L15, M19                  |  |

| VCC_RIN    | R6, E13            | NC       | L2, C1, D1, E1, C2, D2, E2,    |  |

| VCC_ROUT   | L1, E14            |          | E4, E12                        |  |

| AVCC_PHY3V | E10, E11, A17, B17 |          |                                |  |

## 3.2 Pin Characteristics

| 16-bit Card Int | erface | CardBus Card I | nterface | Pin          | Characteristi | cs    | Nata |

|-----------------|--------|----------------|----------|--------------|---------------|-------|------|

| Pin Name        | Dir    | Pin Name       | Dir      | 5Vtolerant   | PwrRail       | Drive | Note |

| TEST            | I      | TEST           | I        |              | 3V            | -     |      |

| HWSPND#         | I      | HWSPND#        | I        | ✓            | 3V            | -     |      |

| SPKROUT         | I/O    | SPKROUT        | I/O      |              | 3V            | 4mA   |      |

| RI_OUT#/ PME#   | O (OD) | RI_OUT#/ PME#  | O (OD)   | ✓            | 3V            | 4mA   |      |

| GBRST#          | I      | GBRST#         | I        |              | 3V            | _     |      |

| UDIO5           | 0      | UDIO5          | 0        | ✓            | 3V            | 4mA   |      |

| UDIO4           | I/O    | UDIO4          | I/O      | ✓            | 3V            | 4mA   |      |

| UDIO3           | I/O    | UDIO3          | I/O      | ✓            | 3V            | 4mA   |      |

| UDIO2           | I/O    | UDIO2          | I/O      | ✓            | 3V            | 4mA   |      |

| UDIO1           | I/O    | UDIO1          | I/O      | ✓            | 3V            | 4mA   |      |

| UDIO0/ SRIRQ#   | I/O    | UDIO0/ SRIRQ#  | I/O      | ✓            | 3V            | 4mA   |      |

| INTA#           | O (OD) | INTA#          | O (OD)   | ✓            | Р             | PCI   |      |

| INTB#           | O (OD) | INTB#          | O (OD)   | ✓            | Р             | PCI   |      |

| INTC#           | O (OD) | INTC#          | O (OD)   | ✓            | Р             | PCI   |      |

| CLKRUN#         | I/O    | CLKRUN#        | I/O      | ~            | Р             | PCI   |      |

| PCIRST#         | I      | PCIRST#        | I        | $\checkmark$ | Р             | _     |      |

| PCICLK          | I      | PCICLK         | I        | √            | Р             | -     |      |

| GNT#            | I      | GNT#           | I        | √            | Р             | -     |      |

| REQ#            | O (TS) | REQ#           | O (TS)   | √            | Р             | PCI   |      |

| AD31            | I/O    | AD31           | I/O      | √            | Р             | PCI   |      |

| AD30            | I/O    | AD30           | I/O      | √            | Р             | PCI   |      |

| AD29            | I/O    | AD29           | I/O      | √            | Р             | PCI   |      |

| AD28            | I/O    | AD28           | I/O      | √            | Р             | PCI   |      |

| AD27            | I/O    | AD27           | I/O      | √            | Р             | PCI   |      |

| AD26            | I/O    | AD26           | I/O      | √            | Р             | PCI   |      |

| AD25            | I/O    | AD25           | I/O      | √            | Р             | PCI   |      |

| AD24            | I/O    | AD24           | I/O      | √            | Р             | PCI   |      |

| C/BE3#          | I/O    | C/BE3#         | I/O      | √            | Р             | PCI   |      |

| IDSEL           | I      | IDSEL          | I        | √            | Р             | -     |      |

| AD23            | I/O    | AD23           | I/O      | ✓            | Р             | PCI   |      |

| AD22            | I/O    | AD22           | I/O      | ✓            | Р             | PCI   |      |

| AD21            | I/O    | AD21           | I/O      | ✓            | Р             | PCI   |      |

| AD20            | I/O    | AD20           | I/O      | ✓            | Р             | PCI   |      |

| AD19            | I/O    | AD19           | I/O      | ✓            | Р             | PCI   |      |

| AD18            | I/O    | AD18           | I/O      | ✓            | Р             | PCI   |      |

| AD17            | I/O    | AD17           | I/O      | √            | Р             | PCI   |      |

| AD16            | I/O    | AD16           | I/O      | √            | Р             | PCI   |      |

| C/BE2#          | I/O    | C/BE2#         | I/O      | √            | Р             | PCI   |      |

| FRAME#          | I/O    | FRAME#         | I/O      | √            | Р             | PCI   |      |

| 16-bit Card Ir | nterface | CardBus Card | Interface | Pin        | Characteristi | cs    | Nata |

|----------------|----------|--------------|-----------|------------|---------------|-------|------|

| Pin Name       | Dir      | Pin Name     | Dir       | 5Vtolerant | PwrRail       | Drive | Note |

| IRDY#          | I/O      | IRDY#        | I/O       | ✓          | Р             | PCI   |      |

| TRDY#          | I/O      | TRDY#        | I/O       | ✓          | Р             | PCI   |      |

| DEVSEL#        | I/O      | DEVSEL#      | I/O       | ~          | Р             | PCI   |      |

| STOP#          | I/O      | STOP#        | I/O       | ~          | Р             | PCI   |      |

| PERR#          | I/O      | PERR#        | I/O       | ~          | Р             | PCI   |      |

| SERR#          | O (OD)   | SERR#        | O (OD)    | ✓          | Р             | PCI   |      |

| PAR            | I/O      | PAR          | I/O       | ✓          | Р             | PCI   |      |

| C/BE1#         | I/O      | C/BE1#       | I/O       | ✓          | Р             | PCI   |      |

| AD15           | I/O      | AD15         | I/O       | ✓          | Р             | PCI   |      |

| AD14           | I/O      | AD14         | I/O       | ✓          | Р             | PCI   |      |

| AD13           | I/O      | AD13         | I/O       | ✓          | Р             | PCI   |      |

| AD12           | I/O      | AD12         | I/O       | ✓          | Р             | PCI   |      |

| AD11           | I/O      | AD11         | I/O       | ✓          | Р             | PCI   |      |

| AD10           | I/O      | AD10         | I/O       | ✓          | Р             | PCI   |      |

| AD9            | I/O      | AD9          | I/O       | ✓          | Р             | PCI   |      |

| AD8            | I/O      | AD8          | I/O       | ✓          | Р             | PCI   |      |

| C/BE0#         | I/O      | C/BE0#       | I/O       | ✓          | Р             | PCI   |      |

| AD7            | I/O      | AD7          | I/O       | ✓          | Р             | PCI   |      |

| AD6            | I/O      | AD6          | I/O       | ✓          | Р             | PCI   |      |

| AD5            | I/O      | AD5          | I/O       | ✓          | Р             | PCI   |      |

| AD4            | I/O      | AD4          | I/O       | ✓          | Р             | PCI   |      |

| AD3            | I/O      | AD3          | I/O       | ✓          | Р             | PCI   |      |

| AD2            | I/O      | AD2          | I/O       | ✓          | Р             | PCI   |      |

| AD1            | I/O      | AD1          | I/O       | ✓          | Р             | PCI   |      |

| AD0            | I/O      | AD0          | I/O       | ✓          | Р             | PCI   |      |

| VCC5EN#        | 0        | VCC5EN#      | 0         | ✓          | 3V            | 4mA   |      |

| VCC3EN#        | 0        | VCC3EN#      | 0         | ✓          | 3V            | 4mA   |      |

| VPPEN0         | 0        | VPPEN0       | 0         | ✓          | 3V            | 4mA   |      |

| VPPEN1         | 0        | VPPEN1       | 0         | ✓          | 3V            | 4mA   |      |

| USBDP          | I/O      | USBDP        | I/O       |            | -             | -     |      |

| USBDM          | I/O      | USBDM        | I/O       |            | -             | -     |      |

| CDATA3         | I/O      | CAD0         | I/O       | ✓          | 3V            | 4mA   |      |

| CD1#           | I (PU)   | CCD1#        | I (PU)    |            | 3V            | _     |      |

| CDATA4         | I/O      | CAD1         | I/O       | ~          | 3V            | 4mA   |      |

| CDATA11        | I/O      | CAD2         | I/O       | ~          | 3V            | 4mA   |      |

| CDATA5         | I/O      | CAD3         | I/O       | ~          | 3V            | 4mA   |      |

| CDATA12        | I/O      | CAD4         | I/O       | ~          | 3V            | 4mA   |      |

| CDATA6         | I/O      | CAD5         | I/O       | ~          | 3V            | 4mA   |      |

| CDATA13        | I/O      | CAD6         | I/O       | ✓          | 3V            | 4mA   |      |

| CDATA7         | I/O      | CAD7         | I/O       | ✓          | 3V            | 4mA   |      |

| CDATA14        | I/O      | _            | _         | ✓          | 3V            | 4mA   |      |

| 16-bit Card In         | nterface | CardBus Card | Interface | Pin          | Characteristi | cs    | Note |

|------------------------|----------|--------------|-----------|--------------|---------------|-------|------|

| Pin Name               | Dir      | Pin Name     | Dir       | 5Vtolerant   | PwrRail       | Drive | Note |

| CE1#                   | 0        | CC/BE0#      | I/O       | ✓            | 3V            | 4mA   |      |

| CDATA15                | I/O      | CAD8         | I/O       | $\checkmark$ | 3V            | 4mA   |      |

| CADR10                 | 0        | CAD9         | I/O       | $\checkmark$ | 3V            | 4mA   |      |

| CE2#                   | 0        | CAD10        | I/O       | $\checkmark$ | 3V            | 4mA   |      |

| OE#                    | 0        | CAD11        | I/O       | ~            | 3V            | 4mA   |      |

| VS1#                   | I/O      | CVS1         | I/O       |              | 3V            | 1mA   |      |

| CADR11                 | 0        | CAD12        | I/O       | √            | 3V            | 4mA   |      |

| IORD#                  | 0        | CAD13        | I/O       |              | 3V            | 4mA   |      |

| CADR9                  | 0        | CAD14        | I/O       | ✓            | 3V            | 4mA   |      |

| IOWR#                  | 0        | CAD15        | I/O       |              | 3V            | 4mA   |      |

| CADR8                  | 0        | CC/BE1#      | I/O       | ✓            | 3V            | 4mA   |      |

| CADR17                 | 0        | CAD16        | I/O       | ✓            | 3V            | 4mA   |      |

| CADR13                 | 0        | CPAR         | I/O       | ✓            | 3V            | 4mA   |      |

| CADR18                 | 0        | -            | -         | √            | 3V            | 4mA   |      |

| CADR14                 | 0        | CPERR#       | I/O (PU)  | ✓            | 3V            | 4mA   | 1    |

| CADR19                 | 0        | _            | I/O (PU)  | √            | 3V            | 4mA   | 1    |

| WE#                    | 0        | CGNT#        | 0         | √            | 3V            | 4mA   |      |

| CADR20                 | 0        | CSTOP#       | I/O (PU)  | √            | 3V            | 4mA   | 1    |

| RDY/ IREQ#             | I (PU)   | CINT#        | I (PU)    | √            | 3V            | _     |      |

| CADR21                 | 0        | CDEVSEL#     | I/O (PU)  | √            | 3V            | 4mA   | 1    |

| CADR16                 | O (TS)   | CCLK         | O (TS)    | √            | 3V            | CB    |      |

| CADR22                 | 0        | CTRDY#       | I/O (PU)  | √            | 3V            | 4mA   | 1    |

| CADR15                 | 0        | CIRDY#       | I/O (PU)  | √            | 3V            | 4mA   | 1    |

| CADR23                 | 0        | CFRAME#      | I/O       | √            | 3V            | 4mA   |      |

| CADR12                 | 0        | CC/BE2#      | I/O       | √            | 3V            | 4mA   |      |

| CADR24                 | 0        | CAD17        | I/O       | ~            | 3V            | 4mA   |      |

| CADR7                  | 0        | CAD18        | I/O       | ✓            | 3V            | 4mA   |      |

| CADR25                 | 0        | CAD19        | I/O       | √            | 3V            | 4mA   |      |

| CADR6                  | 0        | CAD20        | I/O       | ✓            | 3V            | 4mA   |      |

| VS2#                   | I/O      | CVS2         | I/O       |              | 3V            | 1mA   |      |

| CADR5                  | 0        | CAD21        | I/O       | √            | 3V            | 4mA   |      |

| RESET                  | O (TS)   | CRST#        | O (TS)    | $\checkmark$ | 3V            | 2mA   |      |

| CADR4                  | 0        | CAD22        | I/O       | ✓            | 3V            | 4mA   |      |

| WAIT#                  | I (PU)   | CSERR#       | I (PU)    | ✓            | 3V            | _     |      |

| CADR3                  | 0        | CAD23        | I/O       | ✓            | 3V            | 4mA   |      |

| INPACK#                | I (PU)   | CREQ#        | I (PU)    | ✓            | 3V            | _     |      |

| CADR2                  | 0        | CAD24        | I/O       | ✓            | 3V            | 4mA   |      |

| REG#                   | 0        | CC/BE3#      | I/O       | ✓            | 3V            | 4mA   |      |

| CADR1                  | 0        | CAD25        | I/O       | √            | 3V            | 4mA   |      |

| BVD2/<br>SPKR#/<br>LED | I (PU)   | CAUDIO       | I (PU)    | ~            | 3V            | _     |      |

| 16-bit Card In              | nterface                      | CardBus Card                | Interface                     | Pin          | Characteristi | cs    | Note |

|-----------------------------|-------------------------------|-----------------------------|-------------------------------|--------------|---------------|-------|------|

| Pin Name                    | Dir                           | Pin Name                    | Dir                           | 5Vtolerant   | PwrRail       | Drive | NOLE |

| CADR0                       | 0                             | CAD26                       | I/O                           | ✓            | 3V            | 4mA   |      |

| BVD1/<br>STSCHG#/<br>RI#    | I (PU)                        | CSTSCHG                     | I (PD)                        | ~            | 3V            | -     | 2    |

| CDATA0                      | I/O                           | CAD27                       | I/O                           | √            | 3V            | 4mA   |      |

| CDATA8                      | I/O                           | CAD28                       | I/O                           | ✓            | 3V            | 4mA   |      |

| CDATA1                      | I/O                           | CAD29                       | I/O                           | ✓            | 3V            | 4mA   |      |

| CDATA9                      | I/O                           | CAD30                       | I/O                           | ✓            | 3V            | 4mA   |      |

| CDATA2                      | I/O                           | -                           | -                             | ✓            | 3V            | 4mA   |      |

| CDATA10                     | I/O                           | CAD31                       | I/O                           | ✓            | 3V            | 4mA   |      |

| WP/ IOIS16#                 | I (PU)                        | CCLKRUN#                    | I/O (PU)                      | ✓            | 3V            | 4mA   | 1    |

| CD2#                        | I (PU)                        | CCD2#                       | I (PU)                        |              | 3V            | _     |      |

| MDIO00                      | I (PU)                        | MDIO00                      | I (PU)                        | √            | 3V            | _     |      |

| MDIO01                      | I (PU)                        | MDIO01                      | I (PU)                        | √            | 3V            | _     |      |

| MDIO02                      | O (PU)                        | MDIO02                      | O (PU)                        | $\checkmark$ | 3V            | 8mA   |      |

| MDIO03                      | I (PU)                        | MDIO03                      | I (PU)                        | ~            | 3V            | -     |      |

| MDIO04                      | 0                             | MDIO04                      | 0                             | ~            | 3V            | 8mA   |      |

| MDIO05 (SD)<br>(MS)<br>(xD) | O/<br>_/<br>O(PD)             | MDIO05 (SD)<br>(MS)<br>(xD) | O/<br>_/<br>O(PD)             | ~            | 3V            | 8mA   |      |

| MDIO06                      | 0                             | MDIO06                      | 0                             | ~            | 3V            | 8mA   |      |

| MDIO07                      | I                             | MDIO07                      |                               | ~            | 3V            | _     |      |

| MDIO08 (SD)<br>(MS)<br>(xD) | I/O(PU)/<br>O(TS)/<br>O(PU)   | MDIO08 (SD)<br>(MS)<br>(xD) | I/O(PU)/<br>O(TS)/<br>O(PU)   |              | М             | 8mA   |      |

| MDIO09 (SD)<br>(MS)<br>(xD) | I/O(PU)/<br>I/O(PU)/<br>O(PU) | MDIO09 (SD)<br>(MS)<br>(xD) | I/O(PU)/<br>I/O(PU)/<br>O(PU) |              | М             | 8mA   |      |

| MDIO10 (SD)<br>(MS)<br>(xD) | I/O(PU)/<br>I/O/<br>I/O(PD)   | MDIO10 (SD)<br>(MS)<br>(xD) | I/O(PU)/<br>I/O/<br>I/O(PD)   |              | М             | 8mA   |      |

| MDIO11 (SD)<br>(MS)<br>(xD) | I/O(PU)/<br>I/O/<br>I/O(PD)   | MDIO11 (SD)<br>(MS)<br>(xD) | I/O(PU)/<br>I/O/<br>I/O(PD)   |              | М             | 8mA   |      |

| MDIO12 (SD)<br>(MS)<br>(xD) | I/O(PU)/<br>I/O/<br>I/O(PD)   | MDIO12 (SD)<br>(MS)<br>(xD) | I/O(PU)/<br>I/O/<br>I/O(PD)   |              | М             | 8mA   |      |

| MDIO13 (SD)<br>(MS)<br>(xD) | I/O(PU)/<br>I/O/<br>I/O(PD)   | MDIO13 (SD)<br>(MS)<br>(xD) | I/O(PU)/<br>I/O/<br>I/O(PD)   |              | М             | 8mA   |      |

| MDIO14                      | I/O(PD)                       | MDIO14                      | I/O(PD)                       |              | М             | 8mA   |      |

| MDIO15                      | I/O(PD)                       | MDIO15                      | I/O(PD)                       |              | М             | 8mA   |      |

| MDIO16                      | I/O(PD)                       | MDIO16                      | I/O(PD)                       |              | М             | 8mA   |      |

| MDIO17                      | I/O(PD)                       | MDIO17                      | I/O(PD)                       |              | М             | 8mA   |      |

| MDIO18                      | O(PD)                         | MDIO18                      | O(PD)                         |              | М             | 8mA   |      |

| MDIO19                      | O(PD)                         | MDIO19                      | O(PD)                         |              | М             | 8mA   |      |

| 16-bit Card In | terface | CardBus Card I | nterface | Pin        | Characteristi | cs    | Note |

|----------------|---------|----------------|----------|------------|---------------|-------|------|

| Pin Name       | Dir     | Pin Name       | Dir      | 5Vtolerant | PwrRail       | Drive |      |

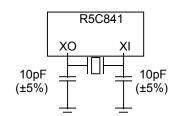

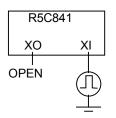

| XI             | I       | XI             | I        |            | AP            |       |      |

| XO             | 0       | ХО             | 0        |            | AP            |       |      |

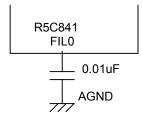

| FIL0           | I/O     | FIL0           | I/O      |            | AP            |       |      |

| CPS            | l(PD)   | CPS            | I(PD)    |            | AP            | 1394  |      |

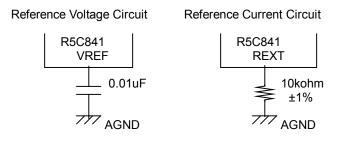

| VREF           | I/O     | VREF           | I/O      |            | AP            |       |      |

| REXT           | I/O     | REXT           | I/O      |            | AP            |       |      |

| TPBN0          | I/O     | TPBN0          | I/O      | ✓          | AP            | 1394  |      |

| TPBP0          | I/O     | TPBP0          | I/O      | ✓          | AP            | 1394  |      |

| TPAN0          | I/O     | TPAN0          | I/O      | ✓          | AP            | 1394  |      |

| TPAP0          | I/O     | TPAP0          | I/O      | ✓          | AP            | 1394  |      |

| TPBIAS0        | I/O     | TPBIAS0        | I/O      |            | AP            | 1394  |      |

| TPBN1          | I/O     | TPBN1          | I/O      | ✓          | AP            | 1394  |      |

| TPBP1          | I/O     | TPBP1          | I/O      | ✓          | AP            | 1394  |      |

| TPAN1          | I/O     | TPAN1          | I/O      | ✓          | AP            | 1394  |      |

| TPAP1          | I/O     | TPAP1          | I/O      | ✓          | AP            | 1394  |      |

| TPBIAS1        | I/O     | TPBIAS1        | I/O      |            | AP            | 1394  |      |

| REGEN#         | 1       | REGEN#         | 1        |            | R             | _     |      |

#### Pin Type

In Type I: Input Pin, O: Output Pin, I/O: Input Out I (PU): Input Pin with Internal Pullup Resister, I (PD): Input Pin with Internal Pulldown Resister, I/O (PU): Input Output Pin with Internal Pulldown Resister, I/O (PD): Input Output Pin with Internal Pulldown Resister, O (TS): Three State Output Pin, O (OD): Open I/O: Input Output Pin,

O (OD): Open Drain Output Pin

#### **Power Rail**

P: VCC\_PCI3V AP: AVCC\_PHY3V R: VCC\_RIN 3V: VCC\_3V M: VCC\_MD3V

#### Drive

PCI: PCI Compliant CB: PCMCIA CardBus PC Card Compliant 1394: IEEE1394a-2000 Compliant

#### Note

Pullup is attached when PC Card Interface is configured as a CardBus Interface Mode.

Pullup or Pulldown is configured according to the type of a card inserted.

| Pin | Media I/F | SD Card | Memory Stick | xD Picture Card |

|-----|-----------|---------|--------------|-----------------|

| 1   | MDIO00    | SDCD#   | _            | XDCD0#          |

| 2   | MDIO01    | —       | MSCD#        | XDCD1#          |

| 3   | MDIO02    | —       | —            | XDCE#           |

| 4   | MDIO03    | SDWP#   | —            | XDR/B#          |

| 5   | MDIO04    | SDPWR0  | MSPWR        | XDPWR           |

| 6   | MDIO05    | SDPWR1  | —            | XDWP#           |

| 7   | MDIO06    | SDLED#  | MSLED#       | XDLED#          |

| 8   | MDIO07    | SDEXTCK | MSEXTCK      | —               |

| 9   | MDIO08    | SDCCMD  | MSBS         | XDWE#           |

| 10  | MDIO09    | SDCCLK  | MSCCLK       | XDRE#           |

| 11  | MDIO10    | SDCDAT0 | MSCDAT0      | XDCDAT0         |

| 12  | MDIO11    | SDCDAT1 | MSCDAT1      | XDCDAT1         |

| 13  | MDIO12    | SDCDAT2 | MSCDAT2      | XDCDAT2         |

| 14  | MDIO13    | SDCDAT3 | MSCDAT3      | XDCDAT3         |

| 15  | MDIO14    | —       | —            | XDCDAT4         |

| 16  | MDIO15    | _       | _            | XDCDAT5         |

| 17  | MDIO16    | _       | _            | XDCDAT6         |

| 18  | MDIO17    | _       | _            | XDCDAT7         |

| 19  | MDIO18    | —       | —            | XDCLE           |

| 20  | MDIO19    | —       | —            | XDALE           |

## • Small Card Pin Assignments

## • ExpressCard Pin Assignments PC Card Pin

#### PC CARD PIN 1-68 ASSIGNMENTS

| Pin | 16bit Card  | CardBus | ExpressCard |

|-----|-------------|---------|-------------|

| 1   | GND         | GND     | GND         |

| 2   | D3 CAD0     |         | —           |

| 3   | D4          | CAD1    | —           |

| 4   | D5          | CAD3    | —           |

| 5   | D6          | CAD5    | —           |

| 6   | D7          | CAD7    | —           |

| 7   | CE1#        | CCBE0#  | —           |

| 8   | A10         | CAD9    | —           |

| 9   | OE#         | CAD11   | —           |

| 10  | A11         | CAD12   | —           |

| 11  | A9          | CAD14   | —           |

| 12  | A8          | CCBE1#  | —           |

| 13  | A13         | CPAR    | —           |

| 14  | A14         | CPERR#  | —           |

| 15  | WE#         | CGNT#   | —           |

| 16  | READY/IREQ# | CINT#   | —           |

| 17  | VCC         | VCC     | VCC         |

| 18  | VPP         | VPP     | —           |

| 19  | A16         | CCLK    | —           |

| 20  | A15         | CIRDY#  | _           |

| Pin      | 16bit Card   | CardBus    | ExpressCard |

|----------|--------------|------------|-------------|

| 21       | A12          | A12 CCBE2# |             |

| 22       | A7           | CAD18      | _           |

| 23       | A6           | CAD20      | _           |

| 24       | A5           | CAD21      | _           |

| 25       | A4           | CAD22      | _           |

| 26       | A3           | CAD23      | _           |

| 27       | A2           | CAD24      | _           |

| 28       | A1           | CAD25      | _           |

| 29       | A0           | CAD26      | _           |

| 30       | D0           | CAD27      | _           |

| 31       | D1           | CAD29      | _           |

| 32       | D2           | RFU        | (PERST#)    |

| 33       | WP/IOIS16#   | CCLKRUN    |             |

| 34       | GND          | GND        | GND         |

| 35       | GND          | GND        | GND         |

| 36       | CD1#         | CCD1#      | CCD1#       |

| 37       | D11          | CAD2       |             |

| 38       | D12          | CAD4       | _           |

| 39       | D13          | CAD6       | _           |

| 40       | D14          | RFU        | _           |

| 41       | D15          | CAD8       | _           |

| 42       | CE2#         | CAD10      |             |

| 43       | VS1#         | CVS1       | CVS1        |

| 44       | IORD#/RFU    | CAD13      | USBD+       |

| 45       | IOWR#/RFU    | CAD15      | USBD-       |

| 46       | A17          | CAD16      | 0000-       |

| 40       | A18          | RFU        |             |

| 48       | A18<br>A19   | CBLOCK#    |             |

| 40       | A19<br>A20   | CSTOP#     | —           |

|          |              | CDEVSEL#   | —           |

| 50       | A21<br>VCC   | VCC        | VCC         |

| 51<br>52 | VCC          | VPP        | VCC         |

|          |              |            |             |

| 53       | A22          | CTRDY#     | CPUSB#      |

| 54       | A23          | CFRAME#    |             |

| 55       | A24          | CAD17      | —           |

| 56       | A25          | CAD19      | -           |

| 57       | VS2#         | CVS2       | CVS2        |

| 58       | RESET        | CRST#      | —           |

| 59       | WAIT#        | CSERR#     | <u> </u>    |

| 60       | INPACK#/RFU  | CREQ#      | <u> </u>    |

| 61       | REG#         | CCBE3#     | <u> </u>    |

| 62       | SPKR#/BVD2   | CAUDIO     | <u> </u>    |

| 63       | STSCHG#/BVD1 | CSTSCHG    | <u> </u>    |

| 64       | D8           | CAD28      | <u> </u>    |

| 65       | D9           | CAD30      | —           |

| 66       | D10          | CAD31      | —           |

| 67       | CD2#         | CCD2#      | CCD2#       |

| 68       | GND          | GND        | GND         |

## Small Card Pin Assignments PC Card Pin (using BAY)

| Pin | 16bit Card  | CardBus | SD Card | Memory Stick | xD Picture<br>Card |

|-----|-------------|---------|---------|--------------|--------------------|

| 1   | GND         | GND     | GND     | GND          | GND                |

| 2   | D3          | CAD0    | _       | _            |                    |

| 3   | D4          | CAD1    | _       | _            | _                  |

| 4   | D5          | CAD3    | _       | —            |                    |

| 5   | D6          | CAD5    | _       | _            | _                  |

| 6   | D7          | CAD7    | _       | _            | _                  |

| 7   | CE1#        | CCBE0#  | _       | —            |                    |

| 8   | A10         | CAD9    | _       | —            | XDWP#              |

| 9   | OE#         | CAD11   | —       | —            | _                  |

| 10  | A11         | CAD12   | _       | —            | XDCE#              |

| 11  | A9          | CAD14   | _       | —            | XDALE              |

| 12  | A8          | CCBE1#  | _       | —            | XDCLE              |

| 13  | A13         | CPAR    | _       | _            | SMWP#              |

| 14  | A14         | CPERR#  | _       | —            | _                  |

| 15  | WE#         | CGNT#   | SDCCLK  | MSCCLK       | XDRE#              |

| 16  | READY/IREQ# | CINT#   | _       | _            | XDCD#              |

| 17  | VCC         | VCC     | VCC     | VCC          | VCC                |

| 18  | VPP         | VPP     | _       | _            | _                  |

| 19  | A16         | CCLK    | _       | _            | _                  |

| 20  | A15         | CIRDY#  |         | _            |                    |

| 21  | A12         | CCBE2#  | _       | _            | _                  |

| 22  | A7          | CAD18   | _       | _            | XDCDAT7            |

| 23  | A6          | CAD20   | _       | _            | XDCDAT6            |

| 24  | A5          | CAD21   | _       | _            | XDCDAT5            |

| 25  | A4          | CAD22   | _       | _            | XDCDAT4            |

| 26  | A3          | CAD23   | SDCDAT3 | MSCDAT3      | XDCDAT3            |

| 27  | A2          | CAD24   | SDCDAT2 | MSCDAT2      | XDCDAT2            |

| 28  | A1          | CAD25   | SDCDAT1 | MSCDAT1      | XDCDAT1            |

| 29  | A0          | CAD26   | SDCDAT0 | MSCDAT0      | XDCDAT0            |

| 30  | D0          | CAD27   | _       | _            |                    |

| 31  | D1          | CAD29   | _       | —            | _                  |

| 32  | D2          | RFU     | _       | —            | _                  |

| 33  | WP/IOIS16#  | CCLKRUN | —       | —            | _                  |

| 34  | GND         | GND     | GND     | GND          | GND                |

| 35  | GND         | GND     | GND     | GND          | GND                |

| 36  | CD1#        | CCD1#   | CCD1#   | CCD1#        | CCD1#              |

| 37  | D11         | CAD2    | —       | —            | —                  |

| 38  | D12         | CAD4    | _       |              | _                  |

| 39  | D13         | CAD6    |         | —            |                    |

| 40  | D14         | RFU     |         | _            |                    |

| 41  | D15         | CAD8    |         | _            |                    |

| 42  | CE2#        | CAD10   | SDCCMD  | MSBS         | XDWE#              |

| 43  | VS1#        | CVS1    | CVS1    | CVS1         | CVS1               |

| 44  | IORD#/RFU   | CAD13   | —       |              |                    |

| 45  | IOWR#/RFU   | CAD15   | —       | _            | _                  |

| Pin | 16bit Card   | CardBus  | SDCard | Memory Stick | xD Picture<br>Card |

|-----|--------------|----------|--------|--------------|--------------------|

| 46  | A17          | CAD16    | —      | —            | —                  |

| 47  | A18          | RFU      | _      | —            | _                  |

| 48  | A19          | CBLOCK#  | —      | —            | —                  |

| 49  | A20          | CSTOP#   | —      | —            | —                  |

| 50  | A21          | CDEVSEL# | —      | —            | —                  |

| 51  | VCC          | VCC      | VCC    | VCC          | VCC                |

| 52  | VPP          | VPP      | _      | —            | _                  |

| 53  | A22          | CTRDY#   | _      | —            | _                  |

| 54  | A23          | CFRAME#  | —      | —            | —                  |

| 55  | A24          | CAD17    | _      | —            | _                  |

| 56  | A25          | CAD19    | _      | —            | _                  |

| 57  | VS2#         | CVS2     | CVS2   | CVS2         | CVS2               |

| 58  | RESET        | CRST#    | _      | —            | _                  |

| 59  | WAIT#        | CSERR#   | _      | MSCD#        | _                  |

| 60  | INPACK#/RFU  | CREQ#    | SDCD#  | —            | —                  |

| 61  | REG#         | CCBE3#   | _      | —            | _                  |

| 62  | SPKR#/BVD2   | CAUDIO   | SDWP#  | —            | XDR/B#             |

| 63  | STSCHG#/BVD1 | CSTSCHG  | _      | —            | _                  |

| 64  | D8           | CAD28    | _      | _            | _                  |

| 65  | D9           | CAD30    | _      | —            | _                  |

| 66  | D10          | CAD31    | _      | _            | _                  |

| 67  | CD2#         | CCD2#    | CCD2#  | CCD2#        | CCD2#              |

| 68  | GND          | GND      | GND    | GND          | GND                |

#### 3.3 **Pin Functions Outline**

In this chapter, the detailed signal pins in the R5C841 are explained. Every signal is divided according to their relational interface.

Card Interface signal pin is multi–functional pin. Card Interface mode is configured automatically by the card insertion; CardBus card or 16-bit card. And the pin function is redefined again.

# mark means the signal is on either active or asserted when the signal is low-level. Otherwise, no-mark means the signal is asserted when the signal is high-level.

The following the notations are used to describe the signal type.

| IN       | Input Pin                                                                                                                                                                                                                                                                                                                                        |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUT      | Output Pin                                                                                                                                                                                                                                                                                                                                       |

| OUT (TS) | Three State Output Pin                                                                                                                                                                                                                                                                                                                           |

| OUT (OD) | Open Drain Output Pin                                                                                                                                                                                                                                                                                                                            |

| I/O      | Input Output Pin                                                                                                                                                                                                                                                                                                                                 |

| I/O (OD) | Input Output Pin (Output is Open Drain)                                                                                                                                                                                                                                                                                                          |

| s/h/z    | Sustained Tri–State is an active low tri–state signal owned and driven by one and only one agent<br>at a time. The agent that drives an s/h/z pin low must drive it high for at least one clock before<br>letting it float. A new agent cannot start driving an s/h/z signal any sooner than one clock after the<br>previous owner tri–state is. |

## 3.3.1 PCI Local Bus interface signals

| Pin Name    | Туре         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |              | PCI Bus Interface Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PCICLK      | IN           | <b>PCI CLOCK:</b> PCICLK provides timing for all transactions on PCI. All other PCI signals are sampled on the rising edge of PCICLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

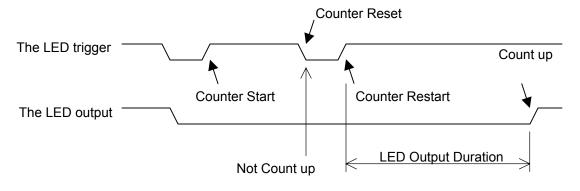

| CLKRUN#     | I/O (OD)     | <b>PCI CLOCK RUN:</b> This signal indicates the status of PCICLK and an open drain output to request the starting or speeding up of PCICLK. This pin complies with Mobile PCI specification. If CLKRUN# is not implemented, then this pin should be tied low. In this case, CardBus clock is controlled by setting of StopClock bit included Socket Control Register. This signal has no meaning for the PC Card16 Cards, the CardBus Cards that does not support CCLKRUN# and not insert Cards to socket. During PCI bus reset is asserted, this pin placed in a high-impedance state. And also, refer to the chapter 4.21 for the LED output.                                     |

| PCIRST#     | IN           | <b>PCI RESET:</b> This input is used to initialize all registers, sequences and signals of the R5C841 to their reset states. PCIRST# causes the R5C841 to place all output buffers in a high-impedance state. The negation of PCIRST# requires no-bounds.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AD [31:0]   | I/O          | ADDRESS AND DATA: Address and Data are multiplexed on the same PCI pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| C/BE [3:0]# | I/O          | <b>BUS COMMAND AND BYTE ENABLES:</b> Bus Command and Byte Enables are multiplexed on the same PCI pins. During the address phase of transaction, C/BE [3:0]# define the bus command. During the data phase C/BE [3:0]# are used as Byte Enables. The Byte Enables are valid for the entire data phase and determine which byte lanes carry meaningful data.                                                                                                                                                                                                                                                                                                                         |

| PAR         | I/O          | <b>PARITY:</b> Parity is even parity across AD [31:0] and C/BE [3:0]#. PAR is stable and valid one clock after the address phase. For data phases, PAR is stable and valid one clock after either IRDY# is asserted on a write transaction or TRDY# is asserted on a read transaction. The master drives PAR for address and write data phases; the target drives PAR for read data phases.                                                                                                                                                                                                                                                                                         |

| FRAME#      | I/O<br>s/h/z | <b>CYCLE FRAME:</b> This signal is driven by the current master to indicate the beginning and duration of an access. FRAME# is asserted to indicate a bus transaction is beginning. While FRAME# is asserted, data transfers continue. When FRAME# is deasserted, the transaction is in the final data phase or has complete.                                                                                                                                                                                                                                                                                                                                                       |

| TRDY#       | l/O<br>s/h/z | <b>TARGET READY:</b> This signal indicates the initialing agent's ability to complete the current data phase of the transaction. TRDY# is used in conjunction with IRDY#. A data phase is completed on any clock both TRDY# and IRDY# are sampled asserted. During a read, TRDY# and IRDY# are sampled asserted. During a read, TRDY# and IRDY# are sampled asserted. During a read, TRDY# and IRDY# are sampled asserted. During a read, TRDY# and IRDY# are sampled asserted. During a complete that valid data is present on AD [31:0]. During a write, it indicates the target is prepared to accept data. Wait cycles are inserted both IRDY# and TRDY# are asserted together. |

| IRDY#       | l/O<br>s/h/z | <b>INITIATOR READY:</b> This signal indicates the initiating agent's ability to complete the current data phase of the transaction. IRDY# is used in conjunction with TRDY#. A data phase is completed on any clock both TRDY# and IRDY# are sampled asserted. During a write, IRDY# indicates that valid data is present on AD [31:0]. During a read, it indicates the target is prepared to accept data. Wait cycles are inserted both IRDY# and TRDY# are asserted together.                                                                                                                                                                                                     |

| STOP#       | I/O<br>s/h/z | <b>STOP:</b> This signal indicates the current target is requesting the master to stop the current transaction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| IDSEL       | IN           | <b>INITIALIZATION DEVICE SELECT:</b> This signal is used as chips select during configuration read and write transactions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DEVSEL#     | l/O<br>s/h/z | <b>DEVICE SELECT:</b> When actively driven, indicates the driving device has decoded its address as the target of the current access. As an input, DEVSEL# indicates whether any device on the bus has been selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PERR#       | l/O<br>s/h/z | <b>PARITY ERROR:</b> This signal is only for the reporting of data parity errors during all PCI transactions except a Special Cycle. The R5C841 drives this output active "low" if it detects a data parity error during a write phase.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Pin Name | Туре     | Description                                                                                                                                                                                                |

|----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |          | PCI Bus Interface Pin Descriptions (Continued)                                                                                                                                                             |

| SERR#    | OUT (OD) | <b>SYSTEM ERROR:</b> This signal is pure open drain. The R5C841 actively drives this output for a single PCI clock when it detects an address parity error on either the primary bus or the secondary bus. |

| REQ#     | OUT (TS) | <b>REQUEST:</b> This signal indicates to the arbiter that the R5C841 desires use of the bus. This is a point to point signal.                                                                              |

| GNT#     | IN       | <b>GRANT:</b> This signal indicates the R5C841that access to the bus has been granted. This is a point to point signal.                                                                                    |

| GBRST#   | IN       | <b>GLOBAL RESET:</b> This input is used to initialize registers for control of PME_Context register. This should be asserted only once when system power supply is on.                                     |

## 3.3.2 System Interrupt signals

| Pin Name                                                                                | Туре     | Description                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                         | •<br>•   | System Interrupt Pin Descriptions                                                                                                                                                                                                                                                                                                                                                              |

| INTA#                                                                                   | OUT (OD) | <b>PCI INTERRUPT REQUEST A:</b> This signal indicates a programmable interrupt request generated from the PC Card interface. This signal is connected to the interrupt line of the PCI bus.                                                                                                                                                                                                    |

| INTB#                                                                                   | OUT (OD) | <b>PCI INTERRUPT REQUEST B:</b> This signal indicates a programmable interrupt request generated from the IEEE 1394 interface. This signal is connected to the interrupt line of the PCI bus.                                                                                                                                                                                                  |

| INTC#                                                                                   | OUT (OD) | <b>PCI INTERRUPT REQUEST C:</b> This signal indicates a programmable interrupt request generated from the Memory Stick interface, the SD Card interface or the xD Picture Card interface. This signal is connected to the interrupt line of the PCI bus.                                                                                                                                       |

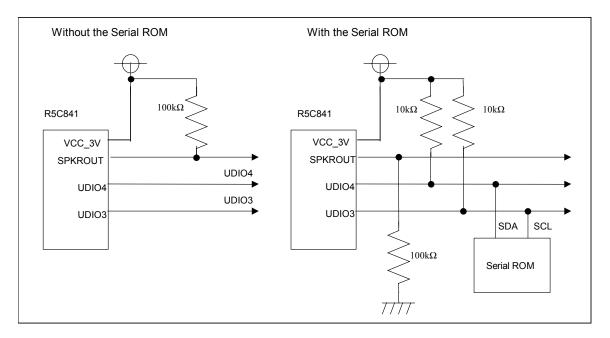

| UDIO0/SRIRQ#<br>UDIO1/GPIO0<br>UDIO2/GPIO1<br>UDIO3/GPIO2<br>UDIO4/GPIO3<br>UDIO5/LED0# | I/O (TS) | USER DEFINABLE INPUT/OUTPUT: These signals can be used as user-definable<br>input/output. Users can define functions such as *GPIO, LED, IRQ and so on for each<br>pin in the PC Card Misc Control 4 Register. For details, refer to "PCI-CardBus Bridge<br>Registers Descripion" in the registers description.<br>*GPIO : General Purpose I/O                                                 |

| RI_OUT#/<br>PME#                                                                        | OUT (OD) | <b>RING INDICATE OUTPUT:</b> When 16-bit card is inserted and Ring Indicate Enable bit in the Interrupt and General Control register is set to one, RI# on the IO Card is forwarded to RI_OUT#.<br><b>POWER MANAGEMENT EVENT:</b> When PME_En bit in Power Management Control/Status register is set or when Power Status is set to any state mode except D0, this signal is assigned as PME#. |

## 3.3.3 16-bit PC Card Interface signals

| Pin Name                 | Туре                                      | Description                                                                                                                                                                                                                                                               |  |  |  |

|--------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                          | 16-bit PC Card Interface Pin Descriptions |                                                                                                                                                                                                                                                                           |  |  |  |

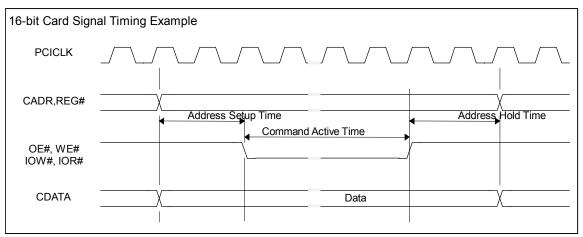

| CDATA [15:0]             | I/O                                       | <b>16-bit Card DATA BUS SIGNALS [15:0]:</b> Input buffer is disabled when the card socket power supply is off or card is not inserted.                                                                                                                                    |  |  |  |

| CADR [25:0]              | OUT (TS)                                  | 16-bit Card ADDRESS BUS SIGNALS [25:0]:                                                                                                                                                                                                                                   |  |  |  |

| IORD#                    | OUT (TS)                                  | 16-bit Card I/O READ:                                                                                                                                                                                                                                                     |  |  |  |

| IOWR#                    | OUT (TS)                                  | 16-bit Card I/O WRITE:                                                                                                                                                                                                                                                    |  |  |  |

| OE#                      | OUT (TS)                                  | 16-bit Card OUTPUT ENABLE:                                                                                                                                                                                                                                                |  |  |  |

| WE#                      | OUT (TS)                                  | 16-bit Card WRITE ENABLE:                                                                                                                                                                                                                                                 |  |  |  |

| CE1#                     | OUT (TS)                                  | 16-bit Card CARD ENABLE 1:                                                                                                                                                                                                                                                |  |  |  |

| CE2#                     | OUT (TS)                                  | 16-bit Card CARD ENABLE 2:                                                                                                                                                                                                                                                |  |  |  |

| REG#                     | OUT (TS)                                  | <b>16-bit Card ATTRIBUTE MEMORY SELECT:</b> This signal selects Attribute Memory access or common memory access during 16bit memory cycle. Attribute memory access is selected when this signal is "low" and common memory access is selected when this signal is "high". |  |  |  |

| READY/<br>IREQ#          | IN                                        | <b>16-bit Card READY/BUSY or INTERRUPT REQUEST:</b> This signal has two different functions. READY/BUSY# input on the memory PC card, and IREQ# input on the I/O card.                                                                                                    |  |  |  |

| WP/<br>IOIS16#           | IN                                        | <b>16-bit Card WRITE PROTECT or CARD IS 16-BIT PORT:</b> This signal has two different functions. Write Protect Switch input on the memory PC card, and IOIS16 input on the I/O card.                                                                                     |  |  |  |

| RESET                    | OUT (TS)                                  | 16-bit Card CARD RESET:                                                                                                                                                                                                                                                   |  |  |  |

| WAIT#                    | IN                                        | 16-bit Card BUS CYCLE WAIT:                                                                                                                                                                                                                                               |  |  |  |

| BVD1/<br>STSCHG#/<br>RI# | IN                                        | <b>16-bit Card BATTERY VOLTAGE DETECT 1 or STATUS CHANGE:</b> This signal has three different functions. The battery voltage detect input 1 on the memory PC card, and Card Status Change#/Ring Indicate# input on the I/O card.                                          |  |  |  |

| BVD2/<br>SPKR#/<br>LED   | IN                                        | <b>16-bit Card BATTERY VOLTAGE DETECT 2 or DIGITAL AUDIO or LED INPUT:</b> This signal has three different functions. The battery voltage detect input 2 on the memory PC card, and SPEAKER# input or LED input on the I/O card.                                          |  |  |  |

| INPACK#                  | IN                                        | 16-bit Card INPUT ACKNOWLEDGE:                                                                                                                                                                                                                                            |  |  |  |